J-Link Plus

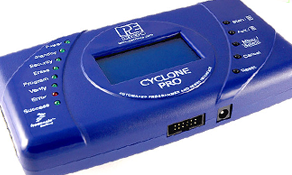

- Segger社が開発したJ-Link PLUSです。

USBインターフェイスのJTAG/SWDエミュレータ

J-Link PLUSは多くのCPUコアに対応しているJTAG電源のUSBです。32バイトRISC CPUをもとに、対応するターゲットCPUと高速で接続します。J-Linkは世界中の何万もの場所で開発や製造(フラッシュプログラミング)の目的のために使われています。

J-LinkはIAR, EWARM, Keil MDK, Rowley CrossWorks, Atollic, TrueSTUDIO, IAR EWRX, Renesas HEW, Renesas e2studioをはじめとするあらゆる主要IDEに対応しています。

全てのモデルを含め、10万以上のJ-Linkがこれまでに販売され、ARMコアや事実上の標準にとって、J-Linkは最も人気のエミュレータと言えるでしょう。

特徴

- フラッシュメモリ内の無制限フラッシュ分断点、RDI, J-Flashのためのライセンス搭載

- 標準のJ-Linkと完全に相互互換可能

- 対応するほとんどの主要なマイコンのフラッシュメモリへのダイレクトなダウンロード

- 対応するCPU:ARM7/9/11, Cortex-M0/M1/M3/M4, Cortex-R4, RX610, RX621, RX62N, RX62T, RX630, RX63N

- ダウンロードの速さ 1メガバイト/秒 以下

- フラッシュメモリへの無制限分断点が可能

- Cortex-Mシステムの外部フラッシュメモリへの分断点の設定は、J-Linkの無制限フラッシュ分断点技術によってのみ可能。

- すべての主要IDEが対応

- 無料ソフトウェアのアップデート、一年間のサポート

- 多様なアプリケーションからのCPUへの同時アクセスが可能

- マルチプラットフォームが可能(Windows, Lunux, Mac OS X によって作動するもの)

- 高性能なエミュレータのファームウェア

- TCP/IPを通してのJ-Linkの遠距離仕様が可能なリモートサーバーが含まれている

- GDBサーバーが含まれている

- 製造フラッシュプログラミングソフトウェアであるJ-Flashが利用可能

- ソフトウェア開発キット(SDK)が利用可能

- 多様なターゲットインターフェイス(JTAG,SWD)に対応

- SWV(シリアル・ワイヤ・ビューアー)、SWO(シリアル・ワイヤ・アウトプット)に対応

- 幅広いボルテージに対応(1.2V,~3,3V,5Vに対応)

- 多様な装置でJTAGチェーンに対応

- 埋め込み式トレースバッファー(ETB)に対応

- 光アイソレーションアダプタを含む様々なアダプタが利用可能

- RDIインターフェイスDLLが利用可能

- プラグ&プレイの両立可能

- USB電源で、電源供給は不要

- アダプティブクロッキングに対応

- すべてのJTAGシグナルが監視され、ターゲットのボルテージが計測可能

- ターゲット電源供給:J-Linkは300ミリアンペアまで供給可能

パッケージ内容

- 標準20ピンコネクタがついたJ-Link(J-Linkとの相互互換可能)

- 20ピンのターゲットリボンケーブル

- USBケーブル

詳細情報

|

一般情報 |

|

|

対応OS |

Microsoft Windows 2000 |

|

電磁両立性 (EMC) |

EN 55022, EN 55024 |

|

作動温度 |

+5°C ... +60°C |

|

保管温度 |

-20°C ... +65 °C |

|

相対湿度 (非縮合) |

Max. 90% rH |

|

機械情報 |

|

|

大きさ (ケーブルを除く) |

100mm x 53mm x 27mm |

|

重さ (ケーブルを除く) |

70g |

|

利用可能なインターフェイス |

|

|

USB インターフェイス |

USB 2.0 |

|

ターゲットインターフェイス |

JTAG 20-pin (14-pin adapter available) |

|

JTAG/SWD インターフェイス 電力面 |

|

|

パワー供給 |

USB powered |

|

ターゲットインターフェイスボルテージ (VIF) |

1.2V ... 5V |

|

ターゲット供給ボルテージ |

4.5V ... 5V (if powered with 5V on USB) |

|

ターゲット供給電力 |

Max. 300mA |

|

リセットタイプ |

Open drain. Can be pulled low or |

|

リセット低レベルアウトプットボルテージ (VOL) |

VOL <= 10% of VIF |

|

ターゲット全体のボルテージ幅(1.2V <= VIF <= 5V) |

|

|

低レベルインプットボルテージ (VIL) |

VIL <= 40% of VIF |

|

高レベルインプットボルテージ (VIH) |

VIH >= 60% of VIF |

|

1.2V <= VIF <= 3.6V |

|

|

低レベルアウトプットボルテージ (VOL) (10 kOhmの時) |

VOL <= 10% of VIF |

|

高レベルアウトプットボルテージ(VOH) (10 kOhmの時) |

VOH >= 90% of VIF |

|

For 3.6 <= VIF <= 5 |

|

|

低レベルアウトプットボルテージ (VOL) (10 kOhmの時) |

VOL <= 20% of VIF |

|

高レベルアウトプットボルテージ(VOH) (10 kOhmの時) |

VOH >= 80% of VIF |

|

JTAG/SWD インターフェイス タイミング |

|

|

JTAGスピード |

Max. 15MHz |

|

SWOサンプリング頻度 |

Max. 7.5MHz |

|

データインプット起動時間 (Trdi) |

Trdi <= 20ns |

|

データインプット終了時間 (Tfdi) |

Tfdi <= 20ns |

|

データアウトプット起動時間 (Trdo) |

Trdo <= 10ns |

|

データアウトプット終了時間 (Tfdo) |

Tfdo <= 10ns |

|

クロック起動時間(Trc) |

Trc <= 3ns |

|

クロック終了時間 (Tfc) |

Tfc <= 3ns |

* J-Link hardware revision 8 and up